FIJI (Fault InJection Instrumenter)

The Fault InJection Instrumenter (FIJI) suite provides an open-source tool flow for performing fault injection tests on chip designs in an FPGA-based environment.

- The tool suite including all source code, documentation and a demo design can be downloaded from here

- An open-access paper that outlines technical details can be found here

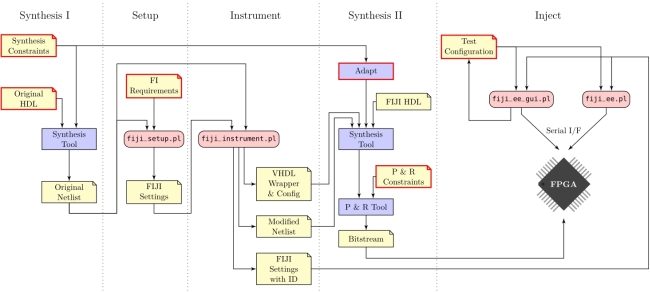

FIJI was developed by the teams of the project VECS and the Josef Ressel Center INES. In contrast to fault injection tests by modification of the RTL source, FIJI targets the already synthesized design at the FPGA primitive level (e.g., Look-up Tables (LUTs), Flip-Flops, and the nets connecting them). Compared to fault injection carried out with the help of partial reconfiguration, FIJI is technology-independent as no knowledge about the bitstream format and the mapping to configuration frames within the FPGA device is required. An overview of the FIJI tool flow is shown in the figure below. Data and actions framed in red have to be supplied by the user.

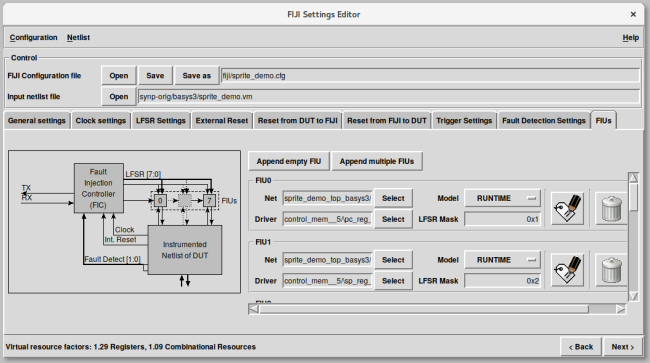

FIJI works by instrumenting a given netlist of a Design under Test (DUT) with fault injection logic according to a predefined fault injection configuration. A parametrized Fault Injection Controller (FIC) is added to the original design. The generation of the fault injection configuration and the parametrization of the FIC is assisted by a graphical user interface but can also be performed manually or by a script, as this information is stored in text files.

Instrumentation is done by the FIJI Instrument tool. This tool modifies the original netlist, and generates wrapper and configuration packages in VHDL. The user is then required to perform synthesis and place&route of the modified design and to download the generated bitstream to the target hardware. Test execution is facilitated by the FIJI Execution Engine (FIJIEE) either via command line or its GUI. These tools communicate with the FIC over a serial interface and instruct the fault injection logic which tests to perform. Both of these tools support the execution of manually specified tests, execution of test sequences, and randomly generated test sequences.

FIJI was developed from 2015-2018 by the University of Applied Sciences Technikum Wien together with the partners from the industry in the project VECS and the Josef Ressel Center INES.