Results: Competence Team for Test and Verification of Dependable Systems

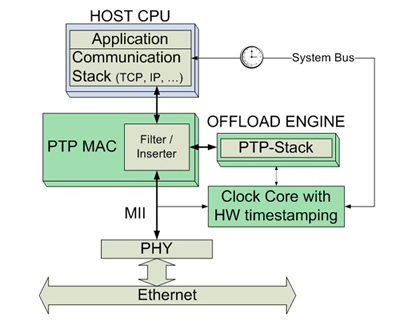

During the past two years, the team members of the Competence Team for Test and Verification of Dependable Systems contributed significanty to a new solution for precision clock synchronisation in networked embedded systems, based upon the 2008 version of the IEEE 1588 standard (Precision time Protocol, PTP). In cooperation with the company Oregano Systems GmbH, who provided IP cores and network components, a hardware- and software infrastructure which completely removes the workload for clock synchronization from a system's main CPU to a dedicated support unit (the so called Offload Engine).

Design, Verification and test of the System on Chip (SoC) and implemenation in an FPGA prototyping environment have been successfully accomplished using state-of-the art Xilinx Virtex 5 platforms. Evaluation of system interoperability could be shown at the PTP plugfest of the ISCPS conference 2008 in Ann Arbour, Michigan.

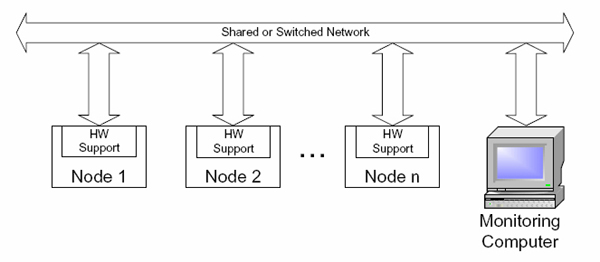

Based upon this highly accurate clock synchronisation solution, a new concept for coordinated debugging in distributed systems could be realised within the second year of the project. This concept comprises an operator PC (OPC) as a central debugging gateway to execute precise halt, single step and trace of individual nodes or groups of nodes in a distrubuted system. This new approach repects the present problems in monitoring and debugging of the highly coordinated networked embedded components commonly used in todays industrial environments due to on-chip support for clock cycle accurate debugging. In the second year of the project (2008), a national patent for this new solution for coordinated distributed debugging has been granted by the austrian patent and trademark office (see publications).

The system topology of the coordinated distributed debugging system solution covers the whole value chain of electronic systems debugging, ranging from on-chip support in hardware to high level integration of a state-of-the art Integrated Developement Environment and widely accepted industry standards for software development and debugging:

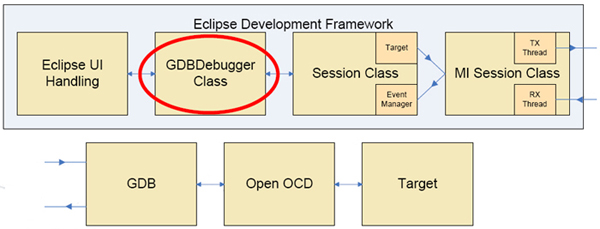

- for source level and symbol information, the GNU debugger (GDB) is utilized, which offers standardized communication protocols to the debugging target, source level debugging support and interfaces to software development tools

- the Eclipse IDE, which represents an extensible software development environment capable of cross development for different CPU architectures was chosen as the debugging front-end, making the coordinated distributed debugging system accessibe fur to user

Furthermore, research results could be integrated in the academic curriculum of the University of Applied Sciences Technikum Wien, where students of the degree programmes Master of Embedded Systems and Bachelor in Electronic Engineering took part in minor design developments in course of master- and bachelor theses.

The dissemination of project results includes participation in various international conferences (see publications).