## **MASTER'S THESIS**

Thesis submitted in partial fulfilment of the requirements for the degree of Master of Science in Engineering

at the University of Applied Sciences Technikum Wien Master of Embedded Systems (MES)

# Development of an OpenOCD compatible Debugger for ARM - CMARMJTAG

by Roman Beneder, BSc 1210 Vienna, Kammelweg 8/Top 4, Austria

Supervisor 1: Dipl.-Ing. Michael Kramer Supervisor 2: Dipl.-Ing. (FH) Martin Zauner Vienna, 15.06.2011

## Declaration

"I confirm that this thesis is entirely my own work. All sources and quotations have been fully acknowledged in the appropriate places with adequate footnotes and citations. Quotations have been properly acknowledged and marked with appropriate punctuation. The works consulted are listed in the bibliography. This paper has not been submitted to another examination panel in the same or a similar form, and has not been published. "

Vienna, 15.06.2011

Place, Date

Beneder Roman

Signature

## Kurzfassung

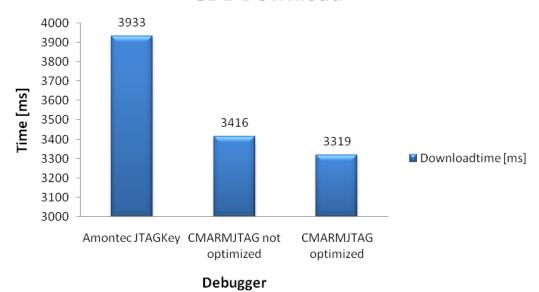

Im Rahmen dieser Arbeit wurde die Soft-/Firmwareentwicklung eines µC (Mikrocontroller) basierenden Debuggers beschrieben, die Funktionalität des entwickelten Debuggers ausführlich getestet und verglichen mit kommerziell verfügbaren Debugger. Der, für den Debugger, verwendete µC ist eine LPC1768 von NXP<sup>1</sup> und basiert auf den ARM<sup>2</sup> Cortex-M3 Core. In dieser Arbeit wurden die grundlegenden Funktionalitäten des Cores erklärt. Es wurden ausschließlich open-source und freie Entwicklungswerkzeuge verwendet. Als Kommunikationsinterface zwischen dem Host und dem Debugger wurde USB<sup>3</sup> (Universal Serial Bus) verwendet und zwischen dem Debugger und der TEP (Target Embedded Platform) wurde JTAG (Joint Test Action Group) verwendet. In dieser Arbeit wird, durch die Komplexität der verwendeten Interfaces, nur auf ausgewählte, projektrelevante Kapitel eingegangen. OpenOCD<sup>4</sup> (Open On-Chip Debugger) wurde verwendet, um mit dem Debugger über USB zu kommunizieren. Der dafür notwendige Interfacedriver wurde implementiert und ausführlich dokumentiert. Die Firmware, welche die Funktionalität des Debuggers implementiert, und sowohl für die Kommunikation zum Host als auch zum TEP zuständig ist, wurde implementiert und ausführlich dokumentiert. Verschiedene Performance Tests wurden durchgeführt, um den entwickelten Debugger mit kommerziell verfügbaren Debugger zu vergleichen. Zum Leistungsvergleich wurde ein FTDI<sup>5</sup>-basierender Debugger der Firma Amontec<sup>6</sup> namens Amontec JTAGKey Tiny herangezogen.

Schlagwörter: Debugger, Cortex-M3, USB, JTAG, FTDI-Chip

- <sup>3</sup> http://www.usb.org/home

- <sup>4</sup> http://openocd.berlios.de/web/

- <sup>5</sup> http://www.ftdichip.com/

- <sup>6</sup> http://www.amontec.com/

<sup>&</sup>lt;sup>1</sup> http://www.nxp.com/

<sup>&</sup>lt;sup>2</sup> http://www.arm.com/

## Abstract

This thesis describes the Soft-/Firmware development of a µC-based debugger. The functionality of the debugger is tested and compared to commercial available debugger. The used µC is a LPC1768 from NXP and is based on the ARM Cortex-M3 core. This thesis highlights the fundamentals of the CM3 (Cortex-M3) core. In this project open-source and free available development tools were used. The communication interface between the host and the debugger is based on USB. To be able to communicate with the TEP, JTAG was used. Due to the complexity of the interfaces, only selected topics of the utilized interfaces were explained. OpenOCD was used to interact with debugger based on USB. OpenOCD can be used to transfer pre-compiled code to the TEP, to control the code execution and to examine the TEP state. To be able to communicate with the debugger an interface driver was developed. The configuration of this driver and its functionality is explained in this thesis. The firmware, running on the debugger, was implemented and is documented in this thesis. Various performance tests were executed to be able to validate the functionality of the debugger. The results of these tests are documented and compared to a commercial available debugger provided by Amontec. The Amontec JTAGKey is a FTDI-based debugger and is applied in many development processes.

## Acknowledgements

I would like to give my appreciation to my supervising tutor Michael Kramer. I want to thank Mr. Kramer for his time, patience and understanding. Furthermore, I want to thank Mr. Kramer for his kind, extensive and specific support during this project. I also want to thank Thomas Kittenberger for his comments and suggestions. I dedicate this thesis to my parents who supported me during my years of study.

## **Table of Contents**

| 1        | Introduction                                 | .5  |

|----------|----------------------------------------------|-----|

| 2        | Project-Specification                        | .7  |

| 3        | Examples of µC-based debugger                | . 9 |

| 4        | Selected Topics of the utilized interfaces1  | 11  |

| 4.1      | USB-Universal Serial Bus1                    | 12  |

| 4.2      | JTAG-Joint Test Action Group2                | 20  |

| 4.2.1    | Test Logic Architecture                      | 20  |

| 4.2.2    | Test Access Port (TAP)2                      | 23  |

| 4.2.3    | Interconnection of components2               | 25  |

| 5        | OpenOCD-Open On-Chip-Debugger in a nutshell2 | 27  |

| 6        | Cortex-M3 core - an overview                 | 30  |

| 7        | Specific project setup                       | 35  |

| 8        | Implementation                               | 37  |

| 8.1      | Integration of a new interface into OpenOCD  | 37  |

| 8.2      | OpenOCD driver description                   | 38  |

| 8.3      | CMARMJTAG firmware description               | 14  |

| 8.3.1    | CM3SYS subfolder description                 | 16  |

| 8.3.2    | CMARM subfolder description                  | 19  |

| 8.3.3    | JTAG subfolder description                   | 50  |

| 8.3.4    | SPI subfolder description                    | 55  |

| 8.3.5    | TIMER0 subfolder description                 | 55  |

| 8.3.6    | USB subfolder description                    | 55  |

| 8.3.7    | Main Application                             | 58  |

| 9        | Test environment6                            | 30  |

| 10       | Performance analyses                         | 32  |

| 10.1     | Performance test configuration6              | 32  |

| 10.2     | Performance test results                     | 33  |

| 10.3     | Performance test utilization6                | 36  |

| 11       | Conclusion & Add-Ons                         | 70  |

| Appendix | ζ                                            | 78  |

## 1 Introduction

This thesis focuses on the development of a JTAG Debugger, which can be used to debug state-of-the-art microcontrollers. These microcontrollers have to have a JTAG interface which gives the debugger the ability to communicate with the debug module of the microcontroller.

Many debuggers are available with different features and abilities. Currently the Technikum Wien<sup>7</sup> uses different microcontrollers in their courses dedicated to embedded system engineering. Some of the  $\mu$ Cs (microcontrollers) have a debugger on-board and some of them are programmed via external debuggers.

The on-board debuggers are often realized with an FTDI Chip<sup>8</sup> which implements the gateway between the USB interface and the JTAG interface. This device can not only be used for this purpose. It can also be used to redirect the hardware RS232 interface of the  $\mu$ C to the USB interface. The FTDI chip has the advantage that this device is especially designed for debugging and programming purposes of various microcontrollers.

The disadvantage is that the FTDI chip is very expensive. It costs  $\in$  8.90 per unit. To get a working debugger based on the FTDI chip it is necessary to use an external EEPROM, which costs  $\in$  0.30, and some passive components. This means that a debugger costs about  $\in$  10.00 and it can only be used as a debugger.

The external debugger is the J-Link from Segger<sup>9</sup> and the ULINK2 from ARM/Keil<sup>10</sup>. The problem is that a limited amount of external debuggers are available on the Technikum Wien and e.g. the J-Link costs  $\in$  248.00 and the ULINK costs  $\in$  289.00.

To gain sustainable knowledge the students of the Technikum Wien should be able to use the applied embedded system while they attend a course dedicated to embedded system engineering. This means that the development environment, the embedded board, and the debugger should be able to be used at home, easy to maintain, and able to be bought by the students. An inquiry with the students has shown that the students are be poised to pay between  $\in$  50.00 till  $\in$  60.00 for such a development equipment.

The mentioned equipment will cost  $\in$  ~400.00 if an external debugger is delivered within the package and cost  $\in$  ~160.00 if the on-board or a debugger based on the FTDI chip is used.

One of the first steps to lowering the costs of the development equipment can be to replace the debugger by a microcontroller which "simulates" a debugger.

<sup>&</sup>lt;sup>7</sup> http://www.technikum-wien.at/

<sup>&</sup>lt;sup>8</sup> http://www.ftdichip.com/

<sup>9</sup> http://www.segger.com/cms/

<sup>&</sup>lt;sup>10</sup> http://www.keil.com/

The usage of a microcontroller used as debugger has the advantage that it is cheaper than the currently used debuggers and the microcontroller can be used for basic tasks in undergraduate courses dedicated to embedded system engineering.

E.g. a Cortex-M3 microcontroller with a minimum of internal memory costs  $\in$  3.44. Additionally some passive external components are required which means that the debugger costs less than the FTDI chip itself. These arguments are the baseline for this thesis.

## 2 Project-Specification

After the introduction it is necessary to specify the features and abilities of the debugger and which functionalities are not supported. To be able to specify the features and abilities it is necessary to analyse the project configuration.

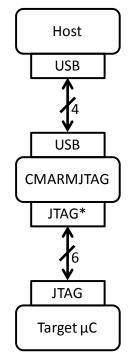

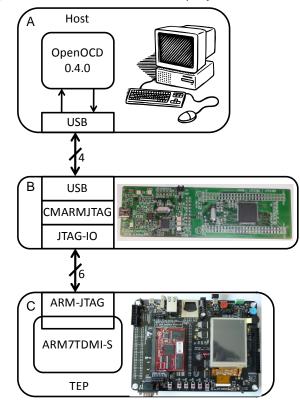

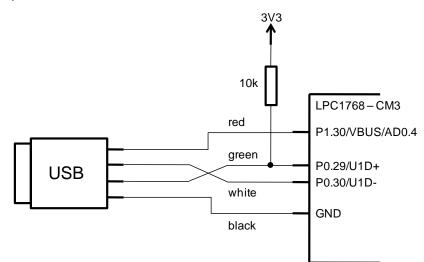

Figure 1 gives an overview over the basic project configuration. The Host illustrates the workstation where the development tools for the Target  $\mu$ C are installed. The interface between the Host and the CMARMJTAG is USB. This interface will be explained in chapter 4. The CMARMJTAG is a state-of-the-art microcontroller which is the gateway between the USB and JTAG interface. The JTAG interface is required to transfer the debug information from the CMARMJTAG to the Target  $\mu$ C. The JTAG\* interface is not the standard JTAG interface of the CMARMJTAG. This interface is necessary to simulate a JTAG interface. In this thesis three possible methods to simulate a JTAG interface are explained.

Figure 1: Basic project configuration

The JTAG Debugger should have the name CMARMJTAG. This name is composed of three phrases.

- CM  $\rightarrow$  Cortex-M

- ARM → ARM Architecture

- JTAG  $\rightarrow$  Interface which is used for the debug communication

The applied microcontroller for this project is an ARM Cortex-M3 from NXP called LPC1768. The used architecture (ARM) and the type of the microcontroller (Cortex-M) can

be found in the abbreviation of the JTAG Debugger. Also the interface which is used between the CMARMJTAG and the target  $\mu$ C (JTAG) can be found in the abbreviation. The JTAG Debugger should:

- be able to integrate into OpenOCD (Open On-Chip-Debugger); OpenOCD is explained in chapter 5

- support ARM-JTAG interface communication

- support variable JTAG speeds

- support real-time debugging

- support in-system programming

- support boundary-scan testing

- support all microcontrollers which are supported into OpenOCD

- use a microcontroller which is:

- o available

- o low-cost

- o and a state-of-the-art microcontroller

For this project the following features are no design goals:

- displaying and storing of Embedded Trace information

- Power Debugging founded by IAR Systems

- a USB/Serial interface

- a SWD interface communication

## 3 Examples of µC-based debugger

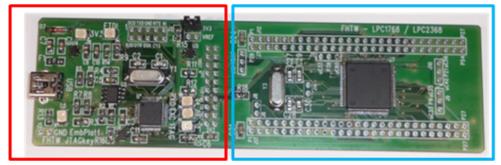

There are projects which are dealing with the development of  $\mu$ C-based debugger. This chapter gives an overview of the related projects.

The SEGGER J-Link [cmp. to p. 24, SEGUM] is a USB powered JTAG emulator which supports a large number of ARM cores. J-Link is based on a 32-bit RISC CPU and is used for development and production purposes. It connects via USB to a PC running Microsoft Windows 2000 or later. J-Link has a built-in 20-pin JTAG connector, which is compatible with the standard 20-pin connector defined by ARM.

The RLink from Raisonance<sup>11</sup> [cmp. to p. 3, RLINK09] is a microcontroller debugger and programmer which supports a range of target interfaces (JTAG, SWD, SWIM, ICC) and connects to 32-bit and 8-bit  $\mu$ Cs to program the target device and debug application in real-time. The standard RLink consists of a ST7365xARxT1  $\mu$ C. This chip is based on an ARM7 core and used in the STM32 Primer1/2 of Raisonance. On the STM Primer1, JTAG is used to program and debug the STM32 and on STM32 Primer2 SWD (Serial Wire Debug) is used.

USBprog<sup>12</sup> [cmp. to USBJTAG07] is a free programming adapter. The adapter is based on an ATmega32 and can be used for programming and debugging AVR and ARM cores, as USB to RS232 converter, as JTAG interface or as simple I/O interface. The adapter allows real-time debugging, setting breakpoints and single stepping.

eStick-JTAG<sup>13</sup> [cmp. to ESJTAG08] is a USB to JTAG adapter to program ARM-based microcontrollers. This adapter allows real-time debugging, in-system programming and boundary-scan testing for embedded targets. This adapter is based on the AT91USB162 of Atmel and was developed at the UAS Technikum Wien.

Table 1 lists  $\mu$ C-based debuggers and FTDI-based debuggers, the prices of them, the theoretical download speed and whether they are supported by OpenOCD or not.

| Name           | Price[€] | Download speed | OpenOCD-Support |

|----------------|----------|----------------|-----------------|

| Segger J-Link* | 248.00   | 12 Mibit/s     | Yes             |

| USBJTAG*       | 44.00    | 960 kibit/s    | Yes             |

| USBprog*       | 34.00    | 4,8 kibit/s    | Yes             |

| JTAGKey-Tiny** | 29.00    | 6 Mibit/s      | Yes             |

| eStick JTAG*   | 15.00    | 70,4 kibit/s   | Yes             |

Table 1: JTAG Debugger

<sup>&</sup>lt;sup>11</sup> http://www.raisonance.com/

<sup>&</sup>lt;sup>12</sup> http://www.embedded-projects.net/index.php?page\_id=135

<sup>&</sup>lt;sup>13</sup> http://code.google.com/p/estick-jtag/

<sup>\*</sup> µC-based debugger

<sup>\*\*</sup> FTDI-based debugger

USBJTAG is a Windows based EJTAG tool for all MIPS core CPUs. It is possible to read and write the memory and program the flash of these CPUs. The USBJTAG is supported by OpenOCD. [cmp. to EJTAG11]

The Segger J-Link is the fastest debugger and offers many features and is supported in OpenOCD. The USBprog is cheaper than the USBJTAG but does not achieve the download rate. It is also supported by OpenOCD. The JTAGKey Tiny provided by Amontec is the most efficient debugger. This debugger is based on the FTDI-Chip and is much faster than the mentioned  $\mu$ C-based debugger at approximately the same price. The eStick-JTAG as already explained is a very low-cost  $\mu$ C-based debugger and achieves a considerable download speed. This debugger is not supported by OpenOCD by default. It is possible to patch OpenOCD with an available patch file to integrate this debugger into OpenOCD. The CMARMJTAG should gain the download speed of the JTAGKey Tiny but with some modifications. After the reset the ARM CPU operates at a core frequency of 4 MHz provided by the internal oscillator. If the CPU runs with the internal oscillator the maximum achievable JTAG clock is 2 MHz. The theoretical download speed mentioned in table 1 is not possible at this configuration.

## **4** Selected Topics of the utilized interfaces

After the analyses of the state-of-the-art debuggers it is necessary to focus on the most important interfaces which are used in this thesis. This chapter focuses on the utilized interfaces. On the one hand the USB interface is required to connect the CMARMJTAG to the Host and on the other hand JTAG is required to transfer data between the target microcontroller and the CMARMJTAG.

#### USB in a nutshell

USB is a handy solution if a computer is used to communicate with a device outside of a computer. The interface is suitable for mass-produced, standard peripheral types as well as small-volume designs, including one-of-a-kind projects. Additionally many microcontrollers based on ARM provide a USB controller. USB offers some benefits for both the users and the developers.

Benefits for Users:

- Ease of Use

- Automatic configuration

- The appropriate software driver is loaded automatically. Otherwise the OS asks for the driver and automatically installs it.

- Easy to connect

- Typical computers have USB ports built in where the external device can be connected easily.

- Easy cables

- USB connectors are small and compact in contrast to typical RS-232 and parallel connectors.

- Hot pluggable

- The USB device can be connected at any time without damaging the host system

- No power-supply required (sometimes)

Benefits for Developers

- Versatility

- USB's four transfer types and three speeds make the interface feasible for many types of peripherals.

- Operating System Support

- The OS (Operating System) automatically detects if a device is attached and removed from a system

- The OS is able to communicate with newly attached devices to find out how to exchange data with them.

- The OS provides a mechanism that enables software drivers to communicate with the computer's USB hardware and the applications that want to access USB peripherals

- Peripheral support

- Every USB peripheral must have a (may be built-in) controller chip that manages the details of USB communications. Some of them are complete microcontrollers or the USB controller is connected externally.

[cmp. p. 2-9, USBC]

#### IEEE Std. 1149.1 in a nutshell

The test logic, the Test Access Port (TAP) and the signals of JTAG are explained in chapter 4.2. The IEEE<sup>14</sup> Std. 1149.1 standard defines test logic that can be an integrated circuit to provide standardized approaches to test the interconnect between integrated circuits once they have been assembled onto a printed circuit board or other substrate, to test the integrated circuit itself, and to observe or modify circuit activity during the component's normal operation.

The test logic consists of a boundary-scan register and other building blocks and is accessed through a Test Access Port (TAP). [cmp. to p1, IEEE1149.1]

## 4.1 USB-Universal Serial Bus

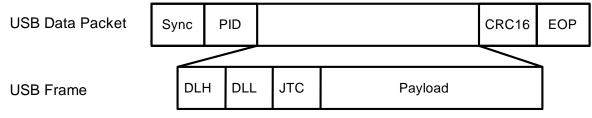

As explained the CMARMJTAG uses two interfaces which are necessary to communicate on the one hand with OpenOCD and on the other hand with the target hardware. One of the interfaces is USB which is used to connect to OpenOCD. OpenOCD is used to emulate the states & functionalities of the debug module of the target hardware on the host machine. This software is described later. This chapter focuses on the descriptor types and does not explain basic transactions and functionalities of the USB interface.

To be able to communicate via USB with the host machine it is necessary to configure the USB-Device. Therefore a device descriptor data structure is used. All USB devices

<sup>&</sup>lt;sup>14</sup> http://www.ieee.org/index.html

respond to requests for the standard USB descriptors. The device must store the information in the descriptors and respond to requests for the descriptors. To be able to understand how the CMARMJTAG is configured and is registered on the host machine it is necessary to explain the required types of descriptors and the configuration possibilities. USB-Descriptors:

- Device Descriptor

- Configuration Descriptor

- Interface Descriptor

- Endpoint Descriptor

- String Descriptor

The descriptors types which are used in the main-file of the firmware are described in detail.

#### **Device Descriptor**

The device descriptor contains basic information about the device. The host first reads the device descriptor when the device is attached. This descriptor provides information which the host needs to retrieve additional information from the device. The device descriptor has 14 fields. Table 1 lists the fields in the order they occur in the descriptor. The descriptor includes information about the descriptor, the device, its configuration and any classes the device belongs to. [cmp. to p.96, USBC]

| Offset | Field             | Size    | Description                                      |

|--------|-------------------|---------|--------------------------------------------------|

| (dec)  |                   | (bytes) |                                                  |

| 0      | bLength           | 1       | Descriptor size in bytes                         |

| 1      | bDescriptorType   | 1       | The constant device                              |

| 2      | bcdUSB            | 2       | USB Specification release number                 |

| 4      | bDeviceClass      | 1       | Class code                                       |

| 5      | bDeviceSubClass   | 1       | Subclass code                                    |

| 6      | bDeviceProtocol   | 1       | Protocol code                                    |

| 7      | bMaxPacketSize0   | 1       | Max. packet size for endpoints                   |

| 8      | idVendor          | 2       | Vendor ID                                        |

| 10     | idProduct         | 2       | Product ID                                       |

| 12     | bcdDevice         | 2       | Device release number                            |

| 14     | iManufacturer     | 1       | Index of string descriptor for the manufacturer  |

| 15     | iProduct          | 1       | Index of string descriptor for the manufacturer  |

| 16     | iSerialNumber     | 1       | Index of string descriptor containing the serNum |

| 17     | bNumConfiguration | 1       | Number of possible configurations                |

Table 2: Device Descriptor [p.97, USBC]

The following descriptions group the information by function. Descriptor:

- **bLength**: The length in bytes of the descriptor

- **bDescriptorType**: The device descriptor type constant

Device:

- bcdUSB: The USB specification that the device and its descriptors comply with in BCD (binary-coded decimal) format.

- **idVendor**: Vendor ID which could be used from the device driver to identify the device.

- **idProduct**: The product ID identifies the device. Each product ID is specific to a vendor ID, so multiple vendors can use the same product ID without conflict.

- **iManufacturer**: An index that points to a string describing the manufacturer. This value is zero if there is no manufacturer.

- **iProduct**: An index that points to a string describing the product. This value is zero if there is no string descriptor.

- **iSerialNumber**: An index that points to a string containing the device's serial number. This value is zero if there is no serial number. Some device classes (such as mass storage) require serial numbers. Serial numbers are useful if users may have more than one identical device on the bus and the host needs to keep track of which is which even after rebooting.

Configuration:

- **bNumConfiguration**: The number of configurations the device supports.

- **bMaxPacketSize0**: The maximum packet size for the standard endpoints. The host uses this information in the requests that follow.

- **bDeviceClass**: For devices whose function is defined at the device level, this field specifies the device's class. Values from 0x01 to 0xFE are reserved for USB's defined classes. The value 0x00 means that the interface descriptor names the class.

- **bDeviceSubclass**: This field can specify a subclass within a class. If bDeviceClass is 0, the bDeviceSubClass must be 0.

- **bDeviceProtocol**: This field can specify a protocol defined by the selected class or subclass.

[cmp. p. 96-101, USBC]

### **Configuration Descriptor**

When the device descriptor, which is explained in the previous chapter, is retrieved, the host can load the device configuration, the parameters for the interface, and the endpoint descriptors. Each device has at least one configuration that specifies the device's features and the abilities. For the CMARMJTAG one configuration is enough, but the declaration of multiple configurations for one device is also possible. Only one configuration is active at a time and every configuration requires a descriptor. The configuration descriptor contains information about the device's use of power and the number of interfaces supported. Each configuration descriptor has subordinate descriptors, including one or more interface descriptors and optional endpoint descriptors.

The configuration descriptor has eight fields. Table 2 lists the fields in the order they occur in the descriptor. The descriptor includes information about the descriptor, the device, its configuration and the device's use of power in that configuration. [cmp. to p. 101, USBC]

| Offset | Field               | Size    | Description                               |

|--------|---------------------|---------|-------------------------------------------|

| (dec)  |                     | (bytes) |                                           |

| 0      | bLength             | 1       | Descriptor size in bytes                  |

| 1      | bDescriptorType     | 1       | The constant configuration                |

| 2      | wTotalLength        | 2       | The number of bytes in the configuration  |

|        |                     |         | descriptor and all of its subordinate     |

|        |                     |         | descriptors                               |

| 4      | bNumInterfaces      | 1       | Number of interfaces in the configuration |

| 5      | bConfigurationValue | 1       | ID for requests                           |

| 6      | iConfiguration      | 1       | Index of string descriptor for the        |

|        |                     |         | configurations                            |

| 7      | bmAttributes        | 1       | Self/bus power and remote wakeup settings |

| 8      | bMaxPower           | 1       | Bus power required, expressed as (maximum |

|        |                     |         | miliamperes/2)                            |

The following descriptions group the information by function. Descriptor:

- **bLength**: The length (in bytes) of the descriptor.

- **bDescriptorType**: The configuration descriptor type constant

- **wTotalLength**: The number of bytes in the configuration descriptor and all of its subordinate descriptors.

Configuration:

- **bConfigurationValue**: Indentifies the configuration for the requests. Must be 1 or higher. A request with a value of zero causes the device to enter the not configured state.

- **iConfiguration**: Index to a string that describes the configuration. This value is zero if there is no string descriptor.

- **bNumInterfaces**: The number of interfaces in the configuration. The minimum is 1.

- bmAttributes: Bit 0=1 if the device is self-powered or 0 if bus-powered. Bit 5=1 if the device supports the remote wakeup feature, which enables a suspended USB device to tell its host that the device wants to communicate. A USB device must enter the Suspend state if there has been no bus activity for 3 milliseconds. If an event at a suspended device requires action from the host, a device with remote wakeup enabled can request the host to resume communications. The other bits in the field are unused. Bits 0 through 4 must be 0. Bit 7 must be 1.

- bMaxPower: Specifies how much bus current a device requires. The bMaxPower value equals one half the numbers of milliamperes required. If the device requires 200 milliamperes, bMaxPower=100. The maximum current a device can request is 500 milliamperes.

[cmp. p. 101-103, USBC]

#### **Interface Descriptor**

After the configuration descriptor the interface descriptor has to be specified. The interface descriptor provides information about a function or feature that a device implements. The descriptor contains class, subclass, and protocol information and the number of endpoints the interface uses.

In the configuration descriptor the number of interfaces is specified, which means that a configuration can have multiple interfaces that are active at the same time. That is a big difference between the configuration and interface descriptor. Only one configuration descriptor can be active at a time, but multiple interfaces can be active at a time. Each interface has its own interface descriptor and subordinate descriptor. Devices that uses isochronous transfers, the transfer type is specified in the next chapter, must have alternate interfaces because the default interface must request no isochronous transfer. Changing interfaces is simpler then changing configurations.

The interface descriptor has nine fields. Table 4 lists the field in the order they occur in the descriptor. [cmp. to p.108, USBC]

| Offset | Field              | Size    | Description                                  |

|--------|--------------------|---------|----------------------------------------------|

| (dec)  |                    | (bytes) |                                              |

| 0      | bLength            | 1       | Descriptor size in bytes                     |

| 1      | bDescriptorType    | 1       | The constant interface                       |

| 2      | bInterfaceNumber   | 1       | Number identifying this interface            |

| 3      | bAlternateSetting  | 1       | Value used to select an alternate setting    |

| 4      | bNumEndpoints      | 1       | Number of endpoints supported, not counting  |

|        |                    |         | standard endpoint                            |

| 5      | bInterfaceClass    | 1       | Class code                                   |

| 6      | bInterfaceSubclass | 1       | Subclass code                                |

| 7      | bInterfaceProtocol | 1       | Protocol code                                |

| 8      | iInterface         | 1       | Index of string descriptor for the interface |

Table 4: Interface Descriptor [p.108, USBC]

The following descriptions group the information by function. Descriptor:

- **bLength**: The number of bytes in the descriptor.

- **bDescriptorType**: The interface descriptor type constant

Interface:

- **iInterface**: Index to a string that describes the interface. This value is zero if there is no string descriptor.

- **bInterfaceNumber**: Identifies the interface. In a composite device, a configuration has multiple interfaces that are active at the same time. Each interface must have a descriptor with a unique value in this field. The default is zero.

- **bAlternateSetting**: When a configuration supports multiple, mutually exclusive interfaces, each of the interfaces has a descriptor with the same value in bInterfaceNumber and a unique value in bAlternateSetting.

- **bNumEndpoints**: The number of endpoints the interface supports in addition to the standard endpoints. For a device that supports only the standard endpoint, bNumEndpoints is zero.

- **bInterfaceClass**: Similar to bDeviceClass in the device descriptor, but for devices with a class specified by the interface. 0xFF indicates a vendor-defined class. Zero is reserved.

- **bInterfaceSubClass**: Similar to bDeviceSubClass in the device descriptor, but for devices with a class defined by the interface. For interfaces that belong to a class, this field may specify a subclass within the class.

- **bInterfaceProtocol**: Similar to bDeviceProtocol in the device descriptor, but for devices whose class is defined by the interface. [cmp. p. 106-108, USBC]

### **Endpoint Descriptor**

Every endpoint that is specified in an interface descriptor has an endpoint descriptor. The standard endpoint never has a descriptor because every device must support the standard endpoint, the device descriptor contains the maximum packet size, and the USB specification defines everything else about the endpoint. Table 4 lists the endpoint descriptor's six fields in the order they occur in the descriptor. [cmp. to p 110, USBC]

| Offset | Field            | Size    | Description                               |

|--------|------------------|---------|-------------------------------------------|

| (dec)  |                  | (bytes) |                                           |

| 0      | bLength          | 1       | Descriptor size in bytes                  |

| 1      | bDescriptorType  | 1       | The constant endpoint                     |

| 2      | bEndpointAddress | 1       | Endpoint number and direction             |

| 3      | bmAttributes     | 1       | Transfer type supported                   |

| 4      | wMaxPacketSize   | 2       | Maximum packet size supported             |

| 5      | bInterval        | 1       | Maximum latency/polling interval/NAK rate |

Table 5: Endpoint Descriptor [p.110, USBC]

The following descriptions group the information by function. Descriptor:

- **bLength**: The number of bytes in the descriptor.

- **bDescriptorType**: The endpoint descriptor type constant

Endpoint:

- bEndpointAddress: Contains the endpoint number and direction. Bits 0 through 3 are the endpoint number. Low-speed devices can have a maximum of 3 endpoints, while full- and high-speed devices can have 16. Bit 7 is the direction: Out=0, In=1. Bits 4, 5, and 6 are unused and must be zero.

- **bmAttributes**: Bits 0 and 1 specify the type of transfer the endpoint support. 00=Control, 01=Isochronous; 10=Bulk, 11=Interrupt. For the standard endpoint, control is assumed.

- wMaxPacketSize: The maximum number of data bytes the endpoint can transfer in a transaction. The allowed values vary with the device speed and type of transfer. Bits 10 through 0 are the maximum packet size, from 0 to 1024 (0 to 1023 in USB1.x). In USB 2.0, bits 12 and 11 indicate how many additional transactions per microframe a high-speed endpoint supports: 00=no additional transactions, 01=additional, 10=2 additional, 11=reserved. In USB 1.x, these bits were reserved and set to zero. Bits 13 through 15 are reserved and must be zero.

- bInterval: Can indicate the maximum latency for polling interrupt endpoints, the interval for polling isochronous endpoints, or the maximum NAK rate for high-speed bulk OUT or control endpoints. The allowed range and how the value is used varies with the device speed, the transfer type, and whether or not the device complies with USB 2.0.

For low-speed interrupt endpoints, the maximum latency equals blnterval in milliseconds. The value may range from 10 to 255.

For all full-speed interrupt endpoints and for full-speed isochronous endpoints on 1.x devices, the interval equals blnterval in milliseconds. For interrupt endpoints, the value may range from 1 to 255. For isochronous endpoints in 1.x devices, the value must be 1. For isochronous endpoints in full-speed 2.0 devices, values from 1 to 16 are allowed, and the interval is calculated as 2<sup>blnterval-1</sup>, allowing a range from 1 milliseconds to 32768 seconds.

For full-speed bulk and control transfers, the value is ignored.

For high-speed endpoints, the value is in units of 125 microseconds, which is the width of a microframe. The value for interrupt and isochronous endpoints may range from 1 to 16, and the interval is calculated as 2<sup>blnterval-1</sup> to allow a range from 125 microseconds to 4096 seconds.

For high-speed bulk OUT and control endpoints, the value indicates the endpoint's maximum NAK rate. This value is relevant when the device has received data and returned ACK, and the host has more data to send in the transfer. By returning ACK, the device is saying that it expects to be able to accept the next transaction's data. If the next data packet arrives and for some reason the device can't accept the packet, the endpoint returns NAK. The bInterval value says that the endpoint will return NAK no more than once in each period specified by bInterval. The value can range from 0 to 255 microframes. A value of zero means that the endpoint will never NAK. The host isn't required to use the maximum-NAK-rate information.

[cmp. p. 108-112, USBC]

#### **String Descriptor**

The string descriptor contains descriptive text which is not necessarily required. The descriptive strings can be used to describe the manufacturer, the product, the serial number, the configuration and the interface. Class- and vendor-specific descriptors can contain indexes to additional string descriptors. The string descriptor defines indexes to various strings. Table 5 shows the descriptor's fields and their purposes.

| Offset | Field              | Size    | Description                                    |

|--------|--------------------|---------|------------------------------------------------|

| (dec)  |                    | (bytes) |                                                |

| 0      | bLength            | 1       | Descriptor size in bytes                       |

| 1      | bDescriptorType    | 1       | The constant string                            |

| 2      | bString or wLangID | Varies  | For string descriptor 0, an array of 1 or more |

|        |                    |         | Language Identifier codes. For other string    |

|        |                    |         | descriptors, a Unicode string.                 |

[cmp. to p.112, USBC]

Table 6: String Descriptor [p.113, USBC]

Descriptor:

- **bLength**: The number of bytes in the descriptor.

- **bDescriptorType**: The string descriptor type constant

String:

When the host requires a String descriptor, the low-byte of the wValue field is an index value. An index value of zero has the special function of requesting language Ids, while other index values request strings that may contain any text.

- wLangID[0...n]: Used in string descriptor 0 only. String descriptor 0 contains one or more 16-bit language ID codes that indicate the languages that the string are available in. The code for English is 0009h, and the subcode for U.S. English is 0004h. These are likely to be the only codes supported by an operating system. The wLangID value must be valid for any of the other strings to be valid. Devices that return no string descriptors must not return an array of language IDs. The USB-IF's web site has a list of defined USB language IDs.

- **bString**: For values 1 or higher, the String field contains a Unicode string. Unicode uses 16 bits to represent each character. With a few exceptions, ANSI character codes 00h through 7Fh correspond to Unicode values 0000h through 007Fh. The strings are not null-terminated. [cmp. p. 112-113, USBC]

## 4.2 JTAG-Joint Test Action Group

The previous chapter described the connection between the debugger and the host. This chapter is intended to provide enough information of the IEEE Std. 1149.1 standard which is necessary to understand the operations of a debugger based on JTAG. Therefore, the test logic architecture, the signals provided by the TAP and the interconnection possibilities are necessary to explain.

### 4.2.1 Test Logic Architecture

This chapter should give an overview over the test logic architecture. The following elements should be included in the test logic architecture:

- a TAP (Test Access Port) described in the next chapter

- a TAP controller

- a instruction register

- and a group of data registers

In figure 2 a conceptual view of the test logic architecture is shown. This figure can be a possible embodiment of the IEEE Std. 1149.1 standard.

Figure 2: Test logic architecture [cmp. p.18, IEEE1149.1]

The TAP receives TCK (Test Clock) and interprets the signals on TMS (Test Mode Select). The TAP controller generates clock or control signals or both as required for the instruction and test data registers and for other parts of the architecture. The signals for the TAP controller are described in the following chapter. The assembled TAP controller signals are Test Access Port.

The instruction register allows the instruction to be shifted into the design. The instruction is used to select the test to be performed or the test data register to be accessed or both. The group of test data registers include a bypass and a boundary-scan register. It optionally can include a device identification register and further test data registers.

The optionally included output stage is necessary to choose which register content is shifted out at the TDO and to retime the signal passing through it to occur at the falling edge of TCK.

[cmp. p. 17-18, IEEE1149.1]

### **TAP** controller

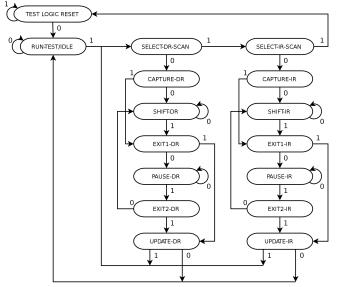

The TAP controller is a synchronous FSM (Finite State Machine) that responds to changes at the TMS and TCK signal of the TAP. It controls the sequence of operations of the circuitry. The mentioned state machine is shown in the figure below.

Figure 3: TAP controller state diagram [cmp. to p.19, IEEE1149.1]

The state transitions of the TAP controller state machine occurs based on the value of TMS at the time of the rising edge of TCK. Actions on the test data registers or the instruction register occurs either the rising or falling edge of TCK in each controller state. The behaviour of the TAP controller is based on the active state. In this thesis the initial states of the synchronous FSM are explained in detail. On [p.20-24, IEEE1149.1], additional or more detailed information of the states is available.

#### **Test-Logic-Reset**

In this state the test logic is disabled and the on-chip logic can operate unhindered. This is achieved by initializing the instruction register to contain the IDCODE instruction or the BYPASS instruction. If TMS is held high for at least five rising edges of TCK it is possible to enter the *Test-Logic-Reset* state from any state in the state machine (shown in figure 3). It is also possible to enter this state, if 0 is applied to TRST\*. If the *Test-Logic-State* is left the *Run-Test/Idle* state is reached.

[cmp. p.20, IEEE1149.1]

#### **Run-Test/Idle**

In this state, activity in selected test logic occurs only when certain instructions are present. For example the RUNBIST instruction causes a self-test of the on-chip system logic to execute in this state. The instruction does not change while he TAP controller is in this state. The controller will remain in this state as long as TMS is kept low. If TMS is logic 1 and a rising edge is applied to TCK the controller will change either in the *Select-DR-Scan*

state if one rising edge occurs or in the *Select-IR-Scan* state if two rising edges on TCK occur. [cmp. p. 20, IEEE1149.1]

### 4.2.2 Test Access Port (TAP)

The Test Access Port is a general-purpose port that can provide access to many test support functions built into a component. The TAP provides a minimum of three input connections and one output connection. An optional fourth input connection provides for asynchronous initialization of the test logic. This chapter focuses on the mentioned I/O signals and their functionality. [cmp. p. 9, IEEE1149.1]

The TAP includes the following signals:

- TCK-Test Clock Input

- TMS-Test Mode Select Input

- TDI-Test Data Input

- TDO-Test Data Output

- TRST\*-Test Reset Input (optional)

- $\circ~$  If the TAP controller is not reset at power-up automatically, a TRST\* input should be provided

The following paragraphs should explain the signals in detail.

### **TCK-Test Clock Input**

This input is required to be able to use the serial test data path between the components independently of the component-specific system clocks. It also permits shifting of test data concurrently with normal system operation of the component. An independent clock ensures that test data can be moved to or from a chip without changing the state of the on-chip system logic. The independent clock is also important if the boundary-scan registers should be usable for board interconnect testing.

The test clock should be a free-running clock with a 50% duty-cycle which can be stopped in some situations for a period. The JTAG standard requires that the TCK can be stopped at 0 indefinitely without causing any change to the state of the test logic. Due to the stopped clock it is necessary that the connected devices retain their state so that the test logic may continue when the clock operation restarts.

The test logic performs their operations at the rising or falling edge of the test clock. This operations have to be completed within a fixed (frequency independent) delay after the occurrence of the relevant change of the TCK. This delay has o be specified by the component supplier.

[cmp p.10-11, IEEE1149.1]

#### **TMS-Test Mode Select Input**

The signal received at TMS is decoded by the TAP controller to control operations. The signal at the TMS is sampled at the rising edge of the test clock. The load at TMS should be as small as possible.

The TAP controller should be forced into the *Test-Logic-Reset* controller state if the TMS pin is undriven. This ensures that normal operation of the complete design can continue without interference from the test logic. If TTL-compatible designs are used, this implies that a pull-up resistor is connected to the TMS line.

It is expected that the bus master - in this project this is the CMARMJTAG - will change the signal driven to the TMS inputs of connected components on the falling edge of TCK. [cmp p. 11, IEEE1149.1]

### **TDI-Test Data Input**

Serial test instructions and data are received by the test logic at TDI. The signal at TDI should be sampled on the rising edge of TCK. Data which is propagated from TDI to TDO without inversion is necessary to simplify the operations of a compatible component. The values which are received at the TDI are clocked into the selected registers (instruction or test data) on the rising edge of TCK. For TTL-compatible designs it is necessary to connect a pull-up resistor on the components TDI pin.

[cmp. p. 12, IEEE1149.1]

#### **TDO-Test Data Output**

TDO is the serial output for test instructions and data from the test logic. A change of the signal at TDO should only occur at the falling edge of TCK. To ensure race-free operation, changes on the TAP inputs (TMS & TDI) are clocked into the test logic at the rising edge of TCK while changes at the TAP output (TDO) occur on the falling edge of TCK. The ability to switch between active and inactive drive is required to allow parallel, rather than serial, connection of board-level test data paths in cases where this is required. In TTL or CMOS technologies this requirement can be met through use of a 3-state output buffer. [cmp. p. 12, IEEE1149.1]

#### **TRST\*-Test Reset Input**

The optional TRST\* provides the ability to asynchronous initialize or reset the TAP controller. If a TRST\* is supported by the TAP, the TAP controller should be able to enter the *Test-Logic-Reset* controller state asynchronously, when a logic 0 is applied to TRST\*. To ensure deterministic operation of the test logic, TMS should be held at 1 while the signal applied at TRST\* changes from 0 to 1 to ensure that the test logic responds predictably. If rising edges occur simultaneously at TRST\* and TCK when a logic 0 is applied to TMS, a race will occur, and the TAP controller may either remain in the *Test-Logic-Reset* controller state or enter the *Run-Test/Idle* controller state.

For TTL-compatible designs it is necessary to connect a pull-up resistor to TRST\* to ensure that in case of a non-terminated TRST\* input, test logic operation can proceed under control of signals applied at the TMS and TCK inputs. It is also possible to disable the test logic by hard-wiring TRST\* to logic 0.

[cmp. p. 13, IEEE1149.1]

#### 4.2.3 Interconnection of components

The previous chapter gave an overview of the signals and defined their requirements and rules according to the IEEE Std. 1149.1 standard. This chapter specifies on the possibilities to interconnect the components compatible to this standard.

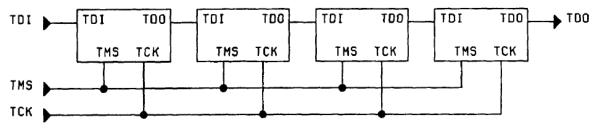

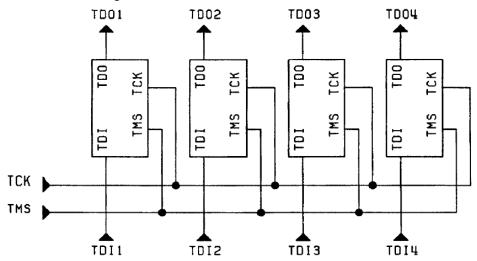

Figure 4, figure 5 and figure 6 illustrate three alternative board level interconnections of components. In each example, the test bus can be controlled by a component that provides an interface to a test bus at the next level of assembly. In this project the device that controls the board-level test bus is referred to as the bus master (CMARMJTAG). Figure 4 contains the minimum required signals which are necessary to assemble a serial path formed by a daisy-chain connection of the serial test data pins (TDI & TDO).

[cmp. p. 14, IEEE1149.1]

Figure 4: Serial connection using one TMS signal [p. 14, IEEE1149.1]

Figure 4 shows four JTAG-compatible devices which are serial connected. In this project the bus slave can be any controller which is supported by OpenOCD. The JTAG signals (TDI, TMS, TCK, TDO) are provided by the CMARMJTAG which acts as a bus master. Additionally the bus master optionally offers a TRST\*, as described in the previous chapter, which is not shown in figure 4.

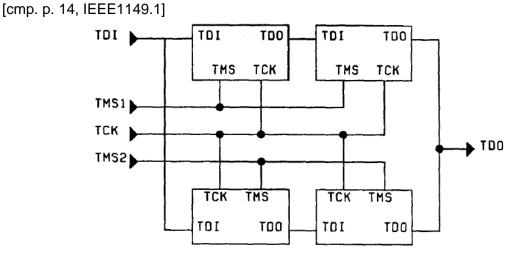

The hybrid serial/parallel connection, shown in figure 5, uses a pair of coordinated TMS signals (TMS1 & TMS2) to ensure that only one serial path is scanning data at a given time.

Figure 5: Connection in two paralleled serial chains [p. 14, IEEE1149.1]

The 3-state output buffer of TDO is used to ensure that only the components that are scanning data have TDO in the active drive state.

Figure 5 shows how to interconnect four bus slaves using multiple independent paths with common TMS and TCK signals.

Figure 6: Multiple independent paths with common TMS & TCK sig. [p. 15, IEEE1149.1]

These paths have separate TDI and TDO signals but can be controlled from common TCK and TMS signals. When choosing a configuration for the board-level interconnection of components conforming to the IEEE Std. 1149.1 standard, it is necessary to consider the capability of test equipment and test pattern generators. It is fully expected that any test equipment and/or test pattern generators that intends to support a test methodology based on the boundary-scan architecture would be able to test the board-level configuration of figure 4, since the degenerated form of this configuration is a single conformant component. Furthermore, some test equipment and/or test pattern generators may not be able to test the board-level configurations of figure 5 and figure 6. [cmp. p. 14, IEEE1149.1]

## 5 OpenOCD-Open On-Chip-Debugger in a nutshell

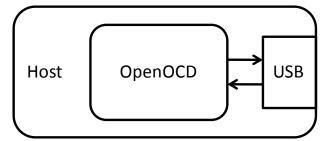

The previous chapters described the interfaces which are used in this project. This chapter explains the program running on the host, shown in figure 1, which uses the USB interface. This chapter gives a basic overview on OpenOCD and is not intended to explain the details. In [3] OpenOCD is explained in detail. Figure 7 shows the host configuration which is used in this project.

Figure 7: Host configuration

OpenOCD runs as a daemon process on the host workstation, making use of a JTAG compliant hardware interface that connects to the target system.[cmp. p.32, OOCD05] This process provides two USB endpoints. One endpoint is configured for input communication and the other endpoint controls the output communication. The endpoints are connected to the USB peripheral of the CMARMJTAG which converts the USB commands provided by OpenOCD into commands which are transferred to the JTAG interface of the target system. The CMARMJTAG also converts the JTAG responds of the target system into USB commands readable for OpenOCD.

OpenOCD is able to load the code in the target memory, to control code execution on the target and examine the target state. [cmp. p. 32, OOCD05]

If there is no code on the target it is necessary to perform initial steps to be able to load the code in the target memory. OpenOCD provides commands to set up the configuration of the target to be able to transfer the compiled code. OpenOCD supports many different flash devices and enables the user to add devices.

Supported Flash devices:

- AT91SAMxxxx from ATMEL

- i.MXxx from Freescale

- LM3Sxxxx from LuminaryMicro

- LPCxxxx from NXP

- OMAPxxxx from Texas Instruments

- S3Cxxxx from Samsung

- STxxxx from STMicroelectronics

OpenOCD offers a possibility to integrate additional JTAG hardware interfaces like the CMARMJTAG and it is possible to change the amount of the debug information during runtime to allow a developer to examine the debugger's behaviour during selected

operations. A configuration file and command line arguments are used to configure the debugger. It is possible to select configuration files via command line arguments, to give the developer the ability to debug multiple targets or multiple configurations, without change or replace the configuration file every time.

#### [cmp. p.32, OOCD05]

The command line interface uses a telnet server embedded in the debugger. The developer can connect to the server process using a telnet client. This allows a single debug system to be used by different users at remote locations. Via the configuration file it is possible to configure the telnet port. If no telnet port is specified, port number 4444 is used.

It is also possible to determine a GDB (GNU Debugger) port for OpenOCD. The standard GDB port number is 3333. Due to this port OpenOCD offers an interface to the GDB. It is possible to use standard GDB commands to configure the target.

Supported GDB commands:

- Poll target state

- o retrieves information about the current target states.

- Architecture state

- o retrieves architecture specific information about the current target state

- Halt

- forces the target into debug state; after halting the target it is possible to examine and modify the target state

- Resume

- makes the target leaving the debug state; target starts executing at the point where it was halted

- Step

- o target executes exactly one instruction

- Reset

- this resets all system functionality, but leaves the debugger in control of the target; it is possible to halt the target after coming out of reset; if no halt occurs the target starts executing from the reset vector

- Set/Get GDB registers

- o it is possible to set and get the content of the core registers

- Read/Write memory

- o it is possible to perform 8-, 16-, or 32-bit accesses to the internal memory of the target; e.g. monitor mwb 0xXXXXXXX 0x00 → this command means Memory Write Byte [Target Address] [Value]

- Add/Remove breakpoints

- Add/Remove watchpoints

[cmp. p.34-35, OOCD05]

OpenOCD supports four different levels of debug information.

- Error messages which are fatal for the program's further execution. Code in OpenOCD → LOG\_ERROR

- Warnings that indicate a problem, but allow the program to continue execution.

Code in OpenOCD → LOG\_WARNING

- Informational messages that are generated during normal program execution. These messages give the user additional information about the debuggers operation. Code in OpenOCD  $\rightarrow LOG_INFO$

- Debug messages, which may occur at a high rate. These messages are used to identify problems during further development of the debugger. Code in OpenOCD → LOG\_DEBUG

[cmp. p. 38, OOCD05]

In the following chapters there are many topics dealing with OpenOCD. Therefore, this chapter highlighted basic functionalities and features.

## 6 Cortex-M3 core - an overview

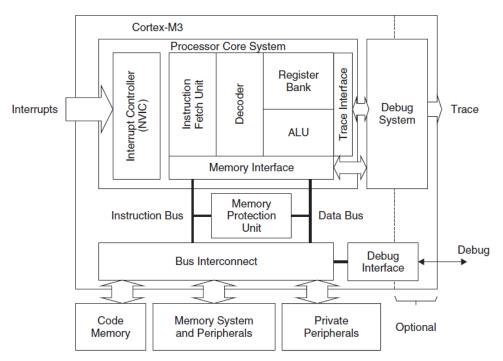

The previous chapter focused on the features and functionalities of OpenOCD which runs on the host workstation. To be able to connect the target hardware to the PC the CMARMJTAG is used. As explained, this device consists of an ARM Cortex-M3. This chapter explains the most important functionalities and features of the Cortex-M3 core. The document [4] provides more detailed information about the core functionality and is used as basis of this chapter.

The Cortex-M3 core is a 32-bit microprocessor which has a 32-bit data-path, a 32-bit register bank and a 32-bit memory interface. This microprocessor is a Harvard architecture, which means it has a separate instruction bus and data bus. The instruction and data buses share the same memory space. The Cortex-M3 core supports both little endian and big endian memory systems. Figure 8 shows a conceptual overview of the core.

[cmp. p. 13, GCM307]

Figure 8: A conceptual view of the Cortex-M3 core [p. 14, GCM307]

The functionality of the built-in components of the CM3 (Cortex-M3) core are explained step by step in the following chapters.

### **Core Registers**

The CM3 processor has the core registers R0-R15. R0-R12 are general purpose registers for data-operations. The CM3 core contains two stack pointers, R13. These two pointers are banked which implies that only one is visible at a time. The MSP (main Stack Pointer) is the default stack pointer and is used by the OS kernel and the exception handlers. The PSP (Process Stack Pointer) is used for user application code. If a subroutine is called the return address is stored in the link register R14. The program counter is stored in R15. Some special registers are also available in the CM3 core. The xPSR register contains the ALU flags, e.g. zero flag, carry flag, execution status etc. The PRIMASK register enables the developer to disable all interrupts expect the NMI (non-maskable interrupt) and HardFault. The FAULTMASK register is used to disable all interrupts of specific priority level or lower priority level. The CONTROL register defines the privileged status and stack pointer selection. [cmp. p. 15-16, GCM307]

#### **Operation Modes**

The CM3 core has two operation modes and two privilege level. If the processor comes out of reset it is in Thread Mode, with privileged access rights. In the privileged state a program has access to all memory ranges. If the CM3 core runs at privileged access level it is possible to write to the control register to switch the mode. If an exception is thrown the processor switches into privileged access level and returns back to the previous access level after execution of the exception. To be able to adjust the control register it is necessary for a user program to go through an exception to program this register. This separation of the access levels is necessary to improve systems reliability and to prevent system configuration registers from being accessed or changed by some untrusted programs.

[cmp. p. 16-17, GCM307]

#### **NVIC-Nested Vectored Interrupt Controller**

The NVIC is closely coupled to the CM3 core and provides a number of features which are explained in this section.

[cmp. p.17, GCM307]

#### **Nested Interrupt Support**

It is possible to define different interrupt priority levels to the external interrupts and to most internal system exceptions. The NVIC compares the priority of the occurred interrupt to the currently running priority level. If the occurred interrupt has a higher priority than the currently running interrupt the processor will override the current running task. [cmp. p.17, GCM307]

### **Vectored Interrupt Support**

The starting addresses of the interrupt service routines (ISR) are located in the vector table in the memory. There is no need to use software to determine and branch to the starting address of the ISR which means that it takes less time to process an interrupt request. [cmp. p.17, GCM307]

### **Dynamic Priority Changes Support**

The priority levels of interrupts can be changed by software during execution. Interrupts which are defined are blocked from activation until the ISR is completed. There is no risk of accidental re-entry.

[cmp. p.17, GCM307]

#### **Reduction of Interrupt Latency**

The CM3 core includes a number of features to lower the interrupt latency. These features are including automatic saving and restoring some register contents, reducing delay from switching from one ISR to another and handling late arrival interrupts.

[cmp. p.17, GCM307]

#### **Interrupt Masking**

It is possible to mask interrupts and system exceptions based on their priority level or using the interrupt mask registers BASEPRI, PRIMASK, and FAULTMASK. This ensures that time-critical tasks can be finished on time without being interrupted. [cmp. p.17, GCM307]

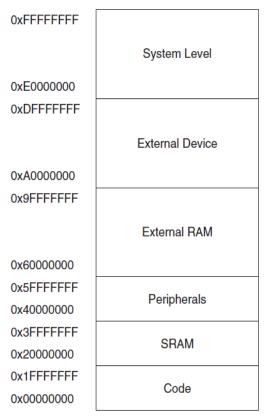

#### **The Memory Map**

The CM3 has a predefined memory map which means that the built-in peripherals can be accessed via simple memory access instructions. The memory map gives the CM3 the ability to be optimized for speed and it is easier to integrate the core in system-on-a-chip (SoC) designs. Figure 9 shows the 4GB memory space of the CM3 core. [cmp. p.19, GCM307]

Figure 9: The CM3 Memory Map [p.19, GCM307]

The System Level memory space includes the private peripherals like the NVIC, the Memory Protection Unit (MPU) registers and the debug components. The External Device section includes the external peripherals and the External RAM section is used for external memory. The SRAM section is used for internal static RAM and the Code section includes the user program code and the exception vector after power-up. The System Level memory region makes it easy to port applications between different CM3 products. [cmp. p. 19, GCM307]

### The Bus Interface

As shown in figure 8 the CM3 provides a code memory bus, which physically consists of two buses. One bus is called I-Code (Instruction Bus) and the other is called D-Code (Data Bus). This bus is optimized for best instruction execution speed. The system bus is used to access memory and peripherals which provides access to the SRAM peripherals, external RAM, external devices and a part of the System Level memory region. For example the debugging components and the NVIC are accessed through the private peripheral bus. [cmp. p. 20, GCM307]

### **The Memory Protection Unit-MPU**

The MPU enables the developer to set up rules for privileged access and user program access. If a rule is violated, a fault exception is generated and it is possible to analyze the problem in the fault exception handler.

Commonly the MPU is used and set up by an operating system, which can define the rule that the OS kernel is able to access privileged data and registers. The MPU can also be used to make memory regions read-only, to prevent accidental erasing of data.

The MPU feature is optional and is determined during the implementation stage of the microcontroller or SoC design.

[cmp. p. 20, GCM307]

### **Debugging Support**

The debugging hardware of the CM3 is based on the CoreSight architecture. Instead of the built-in JTAG interface the CM3 includes a decoupled debug interface module and a bus interface called Debug Access Port (DAP) on core level. The DAP enables external debuggers to access control registers as well as system memory. The bus interface is controlled by the Debug Port (DP) device. There are three integrable DP modules:

- SWJ-DP

- o Supports the JTAG protocol as well as the Serial Wire protocol

- SW-DP

- Supports the Serial Wire protocol

- JTAG-DP

- Supports the JTAG protocol

The manufacturer can also include an Embedded Trace Macrocell (ETM) which allows instruction trace. This information is output via the Trace Port Interface Unit (TPIU) and the host workstation can collect the executed instructions via an external trace-capturing hardware.

[cmp p.24, GCM307]

# 7 Specific project setup

The previous chapters focused on the theoretical basics of the essential parts of the basic project configuration, shown in figure 1. The interfaces JTAG and USB where explained and an overview of the CM3 core operations were given.

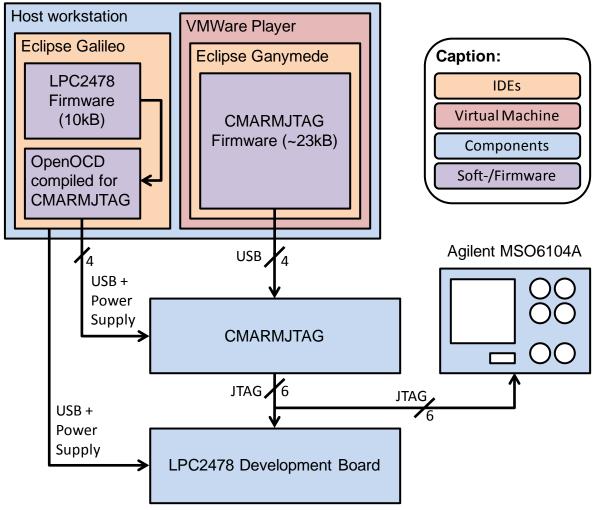

This chapter gives an overview of the specific project configuration. Figure 10 shows the specific project configuration which is used in this project.

Figure 10: Specific Project Configuration

Part A of figure 10 illustrates the host workstation, the OpenOCD and the USB interface. The workstation (Host) is equipped with Ubuntu<sup>15</sup> 10.4 LTS, a state-of-the-art Integrated Development Environment (IDE) and OpenOCD 0.4.0 adapted and compiled for the CMARMJTAG. As IDE, Eclipse<sup>16</sup> Galileo with the GNU ARM and Zylin Embedded CDT plug-ins is used.

Part B of figure 10 shows the prototype of the CMARMJTAG which consists of an ARM Cortex-M3 from NXP called LPC1768. This evaluation board initially was designed to fit onto the baseboard from EmbeddedArtists<sup>17</sup> which provides many external peripherals for microcontrollers based on ARM cores. Additionally the JTAG pins of the LPC1768 are

<sup>&</sup>lt;sup>15</sup> http://ubuntuusers.de/

<sup>&</sup>lt;sup>16</sup> http://www.eclipse.org/

<sup>&</sup>lt;sup>17</sup> http://www.embeddedartists.com/

connected to an external debugger based on the FTDI chip. The external debugger is used to load and debug the firmware for the CMARMJTAG to the LPC1768. This debugging feature enables the developer to precisely design the code for this project.

The LPC1768 is able to provide a CPU clock up to 100MHz and provides 512kB internal Flash memory and 64kB internal SRAM. This  $\mu$ C also has a built-in USB peripheral which is used to communicate with the host workstation. The JTAG-IO interface is not the built-in JTAG interface of the  $\mu$ C. This interface consists of general purpose I/O pins (GPIOs) which are "simulating" a JTAG interface.

Part C of figure 10 shows the Target Embedded Platform (TEP) from EmbeddedArtists. The TEP consists of an ARM7TDMI-S from NXP called LPC2478. This Embedded Platform provides many external peripherals like a Touch Screen Display, a SD-Card Slot, an Ethernet connector, a USB Host/OTG/Device interface, etc. The JTAG interface, called ARM-JTAG in figure 10, is also available on the TEP. This interface is connected to the JTAG-IO interface of the CMARMJTAG.

# 8 Implementation

The previous chapter has given an overview of the specific project configuration. This chapter explains the details of the implementation, describes how to integrate a new interface into OpenOCD, explains the driver which handles the JTAG commands and configures the USB device. Finally the USB firmware library is explained.

# 8.1 Integration of a new interface into OpenOCD

To be able to compile OpenOCD for the CMARMJTAG it is necessary to modify some files in the standard OpenOCD source tree. This chapter describes how to integrate a new interface into OpenOCD. The following files have to be edited to enable the interface for compilation. The root (.) directory is openocd-0.4.0/.

- a) ./configure.in

- b) ./configure

- c) ./config.h

- d) ./README

- e) ./doc/openocd.texi

- f) ./src/Makefile.in

- g) ./src/Makefile.am

- h) ./src/jtag/interfaces.c

- i) ./src/jtag/drivers/Makefile.in

- j) ./src/jtag/drivers/Makefile.am

- k) ./src/jtag/drivers/Makefile

Additionally it is necessary to add a driver file to implement the interface specific routines and to add a basic configuration file for the interface. The interface driver has to be added to ./src/jtag/drivers/. Currently the CMARMJTAG driver is included and named *cmarmjtag.c*. The structure of the driver and the functionalities of the included routines are explained in chapter 8.2. The interface configuration file has to be added to ./tcl/interface/. In this project there already exists a configuration file named *cmarmjtag.cfg*. To ease the integration process of a new interface a patch file is used to auto-integrate the new contents. This patch file is also available in the thesis folder.

## 8.2 OpenOCD driver description

The previous chapter described how to register a new interface into the standard OpenOCD source tree. To be able to access the USB port on the host workstation where the CMARMJTAG is connected and to execute and set up the proper JTAG commands based on the JTAG state machine, it is necessary to develop a driver which provides these functionalities. This chapter describes the structure of the CMARMJTAG driver and explains the most important C-routines of it.

If the JTAG-Debugger is attached to the host, an initial registering procedure is performed. During this procedure the host reads out the required information to locate and enable the new USB device. The device descriptor on the CMARMJTAG provides this information. To check whether the USB device is registered correctly it is necessary to execute the *lsusb* -v / *-less* in the command shell. The following lines show the output for the

#### CMARMJTAG.

| Bus 005 Device 008: 1  | ID ffff: | :0005                 |

|------------------------|----------|-----------------------|

| Device Descriptor:     |          |                       |

| bLength                | 18       |                       |

| bDescriptorType        | 1        |                       |

| bcdUSB                 | 2.00     |                       |

| bDeviceClass           | 255      | Vendor Specific Class |

| <i>bDeviceSubClass</i> | 0        |                       |

| bDeviceProtocol        | 0        |                       |

| bMaxPacketSize0        | 64       |                       |

| idVendor               | 0xffff   |                       |

| idProduct              | 0x0005   |                       |

| bcdDevice              | 1.00     |                       |

| iManufacturer          | 1        | FHTW                  |

| iProduct               | 2        | CMARMJTAG             |

| iSerial                | 3        | 0000:00:1             |

| bNumConfigurations     | 1        |                       |

|                        |          |                       |

Listing 1: Device Descriptor (console output)

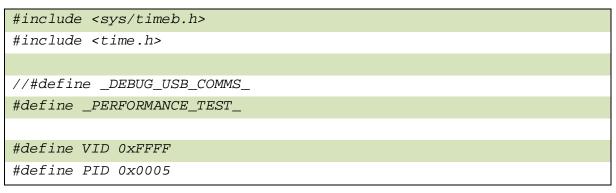

Listing 1 shows the retrieved device descriptor. The vendor identification (VID) and product identification (PID) is configured to 0xffff and 0x0005. These two parameters are necessary to identify the USB device in the CMARMJTAG driver. The manufacturer string, the product string and the serial string are configured via the descriptor in the CMARMJTAG firmware. This device descriptor supports one configuration.

| Configuration Descript | cor:  |  |

|------------------------|-------|--|

| bLength                | 9     |  |

| bDescriptorType        | 2     |  |

| wTotalLength           | 60    |  |

| bNumInterfaces         | 1     |  |

| bConfigurationValue    | 1     |  |

| iConfiguration         | 0     |  |

| bmAttributes           | 0x80  |  |

| MaxPower               | 100mA |  |

|                        |       |  |

Listing 2: Configuration Descriptor (console output)

Listing 2 shows the configuration descriptor of the USB device on the external debugger. The descriptor type field enables the host to identify this descriptor as the configuration descriptor. This configuration descriptor supports one interface and the configuration index is configured to 0. The attributes value indicates that the device is bus powered which means that the host acts as the power supply for the USB device on the CMARMJTAG. The configuration descriptor in the CMARMJTAG firmware configures the power field to 0x32 which means 100mA. For the current project configuration the provided current is adequate. The maximum value for this field is 0xFA: This value is 250<sub>dec</sub> and configures the USB device to 500mA.

| Interface Descriptor: |         |       |          |       |  |

|-----------------------|---------|-------|----------|-------|--|

| bLength               | 9       |       |          |       |  |

| bDescriptorType       | 4       |       |          |       |  |

| bInterfaceNumber      | 0       |       |          |       |  |

| bAlternateSetting     | 0       |       |          |       |  |

| bNumEndpoints         | 2       |       |          |       |  |

| bInterfaceClass       | 255 Ven | dor S | Specific | Class |  |

| bInterfaceSubClass    | 0       |       |          |       |  |

| bInterfaceProtocol    | 0       |       |          |       |  |

| iInterface            | 0       |       |          |       |  |

|                       |         |       |          |       |  |

Listing 3: Interface Descriptor (console output)

Listing 3 shows the interface descriptor of the CMARMJTAG USB device. This interface supports no alternate setting and provides two endpoints which are configured in the endpoint descriptor (Listing 4). The interface index is configured to 0.

| Endpoint Descriptor: |        |              |

|----------------------|--------|--------------|

| bLength              | 7      |              |

| bDescriptorType      | 5      |              |

| bEndpointAddress     | 0x05   | EP 5 OUT     |

| bmAttributes         | 2      |              |

| Transfer Type        |        | Bulk         |

| Synch Type           |        | None         |

| Usage Type           |        | Data         |

| wMaxPacketSize       | 0x0168 | 1x 360 bytes |

| bInterval            | 0      |              |

| Endpoint Descriptor: |        |              |

| bLength              | 7      |              |

| bDescriptorType      | 5      |              |

| bEndpointAddress     | 0x82   | EP 2 IN      |

| bmAttributes         | 2      |              |

| Transfer Type        |        | Bulk         |

| Synch Type           |        | None         |

| Usage Type           |        | Data         |

| wMaxPacketSize       | 0x0168 | 1x 360 bytes |

| bInterval            | 0      |              |

Listing 4: Input / Output Endpoint Descriptor (console output)

The endpoint descriptor, shown in Listing 4, is necessary to configure the required endpoints of the USB device. The first endpoint is an out endpoint.

The communication direction is configured from the host point of view. This means via the out endpoint on the host, data can be written to the CMARMJTAG. The out endpoint of the USB device of the external debugger is configured to address 0x05. But the CMARMJTAG receives data via this endpoint.

The read endpoint of the host receives data from the external debugger. But the read endpoint of the CMARMJTAG sends data to the host. The out endpoint address is configured to 0x05 and the transfer type is configured to bulk transfers. The out endpoint is used to transfer data and has a maximum packet size of 360 bytes because during a debugging session no more than 360 bytes are transmitted via the TDO pin.

The second endpoint is an in endpoint or read endpoint. This endpoint has the address 0x82. The read endpoint transfer type is configured to bulk transfer and is able to transfer a maximum of 360 bytes in a packet. The packet length is the same length as the buffer size of the external debugger.

| Device | Status:  | 0x0000 |

|--------|----------|--------|

| (Bus   | Powered) |        |

Listing 5 shows the device status. After attachment of the USB device and successful registration the device status should be 0x0000. In the CMARMJTAG driver there are some *#defines* which are necessary to provide parameters for the USB device on the host and to determine the speed limits of the JTAG clock. The interface mapping between the standard OpenOCD low-level functions is done via the interface structure shown in Listing 6.

| <pre>struct jtag_interface cmarmjtag_interface =</pre> |

|--------------------------------------------------------|

| {                                                      |

| .name = "cmarmjtag",                                   |

| .commands = cmarmjtag_command_handlers,                |

| .execute_queue = cmarmjtag_execute_queue,              |

| .speed = cmarmjtag_speed,                              |

| .speed_div = cmarmjtag_speed_div,                      |

| .khz = cmarmjtag_khz,                                  |

| .init = cmarmjtag_init,                                |

| .quit = cmarmjtag_quit,                                |

| };                                                     |

Listing 6: CMARMJTAG interface structure (code snippet)

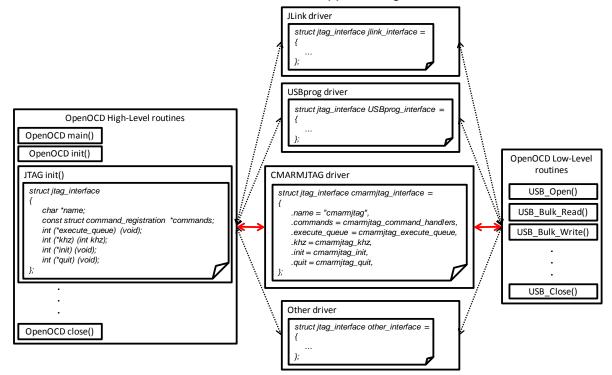

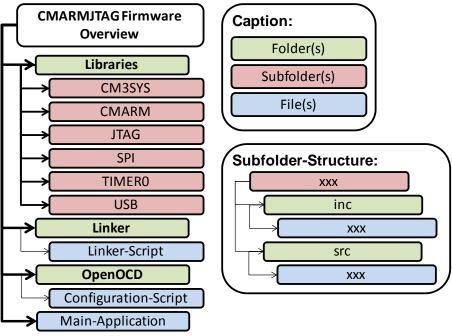

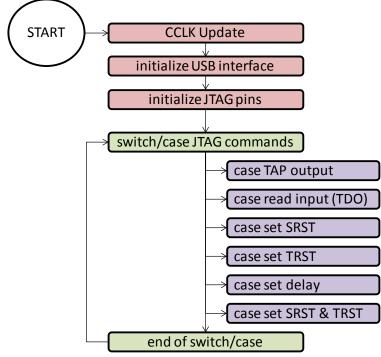

This interface structure enables the developer to implement interface specific functions accessible via OpenOCD. Figure 11 gives an overview of the CMARMJTAG driver structure. The routines *speed()* and *speed\_div()*, shown in Listing 6, are present in the driver but not used. Thus these routines do not appear in figure 11.

Figure 11: CMARMJTAG Driver Overview